## Q: How can I test memories with ETS2k?

## Testing a Memory Under ETS2k

The Memory Test feature of the ETS is possible because of the tremendous versatility of the HiLevel proprietary gate arrays that control the ETS pin electronics. The powerful ETS2k software redefines the functions of these chips so that very deep memory devices can be tested using very few vectors. When using the ETS for Memory Test the software takes control of the vectors and the pattern generator program, so it is important that you not modify these resources manually.

It is very important to plan ahead for Memory Test, particularly when building up your DUT board. This is due to the way in which the pin electronics boards are assigned for specific purposes. PE board #1 (pins 1-32) is used for the memory address pins of your device. ETS2k will control these pins like a counter, sequencing through memory addresses as part of a pattern generator loop. PE board #2 (pins 33-64) will function as the data I/O pins to the memory device under test. PE board #3 (pins 65-96) provides control pin functions for your memory device, such as output enables, chip enables and read/write pins.

You can use the PinList import feature to assign your pins and names, or do it manually from the Main Test setup window. Just be sure to assign pins according to their types as illustrated in the above paragraph, and in accordance with your DUT board wiring. Here are the main steps in preparation. You can also use the ETS2k User Manual for more assistance.

Begin the setup by checking the Memory Test box on the "Modes" area of the Main Setup window:

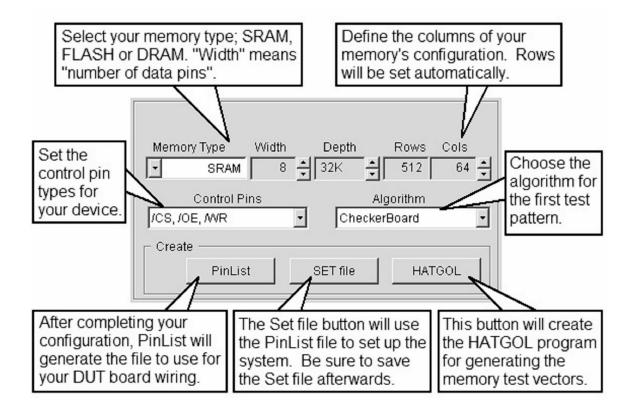

Now the Memory Setup window appears in the lower right corner of the Main Setup window. This is where you will define the basic characteristics of your device and also access other Memory test features.

There are three suggested Control Pin configurations. Don't worry if none match your configuration exactly; you can edit the PinList file to match your needs.

| Control Pins                               |   |

|--------------------------------------------|---|

| /CS, /OE, /WR                              | • |

| ICS, IOE, IWR                              |   |

| /CS1, CS2, /OE, /WR<br>/CS, /OE, /CLK, /WR |   |

| /CS, /OE, /CLK, /WR                        |   |

The ETS2k software supports these standard algorithms. Just use the scroll buttons to select one for your first test. Later, you can select different ones to create more vector sets.

| Algorithm          |   |

|--------------------|---|

| CheckerBoard       | - |

| WalkingOnes        | ~ |

| WalkingZeros       |   |

| MarchingOnes       | = |

| MarchingZeros      |   |

| Sequential Address | * |

The PinList shown on the next page is the result of clicking the PinList button after your configuration has been defined. Save this file after you have typed in your DUT pin numbers and made any other changes. Then press the Set file button to import the PinList.

| ; SysCh     | Pin#        | Name   | Grp                                                                     | Туре |                                                          |

|-------------|-------------|--------|-------------------------------------------------------------------------|------|----------------------------------------------------------|

| 16          | ?           | ADR15  | 1                                                                       | SMA  | ; DISCONNECTED                                           |

| 15          | ?           | ADR14  | 1                                                                       | SMA  | Λ                                                        |

| 14          | ?           | ADR13  | 1                                                                       | SMA  |                                                          |

| 13          | ?           | ADR12  | 1                                                                       | SMA  | In our example,                                          |

| 12          |             | ADR11  | 1                                                                       | SMA  |                                                          |

| 11          | ?           | ADR10  | 1                                                                       | SMA  | channel 16 is                                            |

| 10          | ?           | ADR9   | 1                                                                       | SMA  | disconnected                                             |

| 9           | ?           | ADR8   | 1                                                                       | SMA  | because Address                                          |

| 8           | ?           | ADR7   | 1                                                                       | SMA  |                                                          |

| 7           | ?           | ADR6   | 1                                                                       | SMA  | bit 15 is not needed                                     |

| 6           | ?           | ADR5   | 1                                                                       | SMA  | for a 32K depth.                                         |

| 5           | ?           | ADR4   | 1                                                                       | SMA  | ior a bert deptil.                                       |

| 4           | ?           | ADR3   | 1                                                                       | SMA  |                                                          |

| 3           | ?           | ADR2   | 1<br>1                                                                  | SMA  |                                                          |

| 3<br>2<br>1 | ?           | ADR1   | 1                                                                       | SMA  | a general state of the second state of the second state. |

| 1           | ?           | ADRØ   | 1                                                                       | SMA  | You will set leading                                     |

| 40          | ?           | DATA7  | 2                                                                       | SMD  | and trailing edges                                       |

| 39          | ?????????   | DATA6  | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | SMD  | for the write pulse.                                     |

| 38          | ?           | DATA5  | 2                                                                       | SMD  | If your write pin is                                     |

| 37          | ?           | DATA4  | 2                                                                       | SMD  | -                                                        |

| 36          | ?           | DATA3  | 2                                                                       | SMD  | active hi, then use                                      |

| 35          | ?           | DATA2  | 2                                                                       | SMD  | RZ format.                                               |

| 34          | ?           | DATA1  | 2                                                                       | SMD  |                                                          |

| 33          | ?           | DATAØ  | 2                                                                       | SMD  |                                                          |

| 65          | ?           | /WRITE | 3                                                                       | I    | ; make this R1 signa                                     |

| 66          | ?<br>?<br>? | /OE    | 4                                                                       | I    |                                                          |

| 67          | ?           | /cs    | 5                                                                       | I    |                                                          |

| \$DISCON    | NECT PI     | N 16   |                                                                         |      |                                                          |

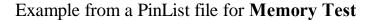

The pin TYPEs SMA and SMD in the PinList file mean "Split Memory Address" and "Split Memory Data", as can be seen as the Pin Direction in the Pin Setup area of the Main Setup window. Do not change these settings.

You will also notice that for the Address and Data groups (groups 1 and 2) that the timing section of the Main Setup window has changed. The "Trailing Edge" field is now called "Memory Edge".

Now you can define your DUT power supplies, logic levels, and test rate. You will see that the sequencing mode is set to Memory Test. Do not change this setting. Save your Set file for future loading.

| Timing —    |     |       |      |

|-------------|-----|-------|------|

| Strobes     | Dly | Value | Unit |

| Leading     | 5   | 4 :   | % -  |

| Memory Edge |     | 75    | % -  |

| Ru                  | in Setup      |            |   |

|---------------------|---------------|------------|---|

| Test Rate           | Test ExtClock |            |   |

| Freq (MHz) 10.000   | Clock Source  | Internal   | • |

| Period (ns) 100.000 | Sequencing    | MemoryTest | - |

Select a Test Pattern from the Algorithm box in the MemoryTest Setup section. For your first pattern, it is common practice to use CheckerBoard.

| Algorithm          |   |

|--------------------|---|

| CheckerBoard       | • |

| WalkingOnes        | ~ |

| WalkingZeros       |   |

| MarchingOnes       | = |

| MarchingZeros      |   |

| Sequential Address | * |

If you open the Vectors window, you can see your assigned pin groups displayed. You'll also see random, unmeaningful data as the vectors (see below). Press the HATGOL button on the Memory Test section of the Main Setup window. This action will cause the Comment field of the Vectors window to be filled with the HATGOL statements necessary to translate vectors for the selected test pattern, as can be seen in example on the next page. Refer to the HATGOL manual for details about these instructions and commands in the Comment field.

| Vector<br>Address<br>(Hex)                                                                                                               | Program                                                      | /<br>W<br>R<br>I//<br>TOC<br>Address Data EES                                                                                                                                                                                                                                                                                                                         | Comments |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 000000<br>000001<br>000002<br>000003<br>000004<br>000005<br>000006<br>000007<br>000008<br>000008<br>000008<br>000008<br>000008<br>000000 | NOOP<br>NOOP<br>NOOP<br>NOOP<br>NOOP<br>NOOP<br>NOOP<br>NOOP | ????? FFFX ?? XF 1 Z 1   ?Z?? FFXX ?? FX Z 1   ?Z?? XFFF ?? FF Z Z   ??Z? XXFF ?? FF Z Z   ??Z? XFFF ?? FF Z Z   ??Z? FXFX ?? FF Z Z   ??Z? FXFX ?? FF Z Z   ?XZ? FXFX ?? FF Z Z   ?XZ? FXFX ?? FF Z Z   ?XZ? FXFX ?? FF Z Z   ?XZZ FXFX ?? FF Z Z   ?Z? FXXF ?? FF Z Z   ?Z?? FXXF ?? FF Z Z   ?Z?? FXXF ?? FF Z Z   ?Z?? FXFF ?? FF Z 1   ZZ?? FXXF ?? FF <td></td> |          |

Vector Window Before HATGOL Button is Pressed

In the vectors Comment field, some definitions may need to be modified prior to translating, i.e. 'WRITE', 'READ', and 'default'. Each of these is preceded with the '#define' statement. Initially these will be all ones. The order of bits for these binary values is determined by the 'consign' statement, which is used to assign the appropriate control pins to the 'Control' group referenced by the HATGOL 'control' statement. For example, if groups /WRITE, /OE, and /CS (all active low) are groups 3, 4, and 5 respectively, and are 'consigned' as 3 4 5, then modify the 'WRITE' definition from 0b\_111 to 0b\_010 and

modify the 'READ' definition fomr 0b\_111 to 0b\_100 ('0b\_' denotes binary). Reference the HATGOL Manual for more detailed information.

| Vector<br>Address Program<br>(Hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /<br>W<br>R<br>I / /<br>T O C<br>Address Data E E S                                                                                                                                                                                                                                                                                                | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000000   NOOP     000001   NOOP     000002   NOOP     000003   NOOP     000004   NOOP     000005   NOOP     000006   NOOP     000007   NOOP     000008   NOOP     000007   NOOP     000008   NOOP     000010   NOOP     000011   NOOP     000012   NOOP     000013   NOOP     000014   NOOP     000015   NOOP     000016   NOOP     000017   NOOP     000018   NOOP     000019   NOOP     0000100   NOOP     000011 | ?Z?? FFFX ?? XF 1 Z   ?Z?? FFXX ?? FY Z Z   ?Z?? XFFF ?? FF Z Z   ?Z?? XFFF ?? FF Z Z   ?Z?? FXXF ?? FF Z Z   ???Z FXFF ?? FF Z Z   ???Z FXFF ?? FF Z Z   ???Z FXFF ?? FF Z Z   ???Z FXF ?? FF Z Z   ???? FFFX ?? FF Z Z   ???? FFX ?? F Z Z   ???? FFX ?? F Z | HATGOL MemoryTest Checkerboard<br>jmp \$Start<br>consign 3 4 5<br>#conf width 8<br>#define depth 32K-1<br>#define repeats 512/2-1<br>#define repeats 512/2-1<br>#define mREAD 0b_100<br>#define default 0b_111<br>#define default 0b_111<br>#define Complement ones<br>control default all<br>Control default all<br>control WRITE, addr = @ + 1. DATA = ~@<br>loop PageSize<br>control WRITE, addr = @ + 1. DATA = ~@<br>return<br>:Read_2_Pages<br>loop rd_count jmp<br>control READ, compare InitData, addr = @ + 1, jmp -1 |

Vector Window After HATGOL Button is Pressed

After making any modifications, merely press the 'Translate' button labeled [HT] on the main toolbar (top of window). This action will cause the HATGOL to be translated into vectors, as seen on the next page. The HATGOL program can be edited at any time for changes, but you must hit the "HT" button again to translate your changes into vectors.

| Vector<br>Address<br>(Hex)                                                                                                                   | Program                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /<br>W<br>R<br>I / /<br>T O C<br>Address Data E E S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Comments                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000000<br>00001<br>000012<br>00003<br>00003<br>00005<br>00006<br>00006<br>000007<br>000008<br>000000<br>000000<br>000000<br>000000<br>000000 | NOOP     NOOP | 0000   XXXX   00   XX   1   1     0000   XXXX   00 <td>HATGOL MemoryTest Checkerboard<br/>jmp %Start<br/>consign 3 4 5<br/>#conf width 8<br/>#define depth 32K-1<br/>#define repeats 512/2-1<br/>#define repeats 512/2-1<br/>#define wRITE 0b_100<br/>#define default 0b_111<br/>#define Gomplement 0xff<br/>control default all<br/>:Write_2_Pages</td> | HATGOL MemoryTest Checkerboard<br>jmp %Start<br>consign 3 4 5<br>#conf width 8<br>#define depth 32K-1<br>#define repeats 512/2-1<br>#define repeats 512/2-1<br>#define wRITE 0b_100<br>#define default 0b_111<br>#define Gomplement 0xff<br>control default all<br>:Write_2_Pages |

| 000021<br>000022<br>000023<br>000024<br>000025<br>000026                                                                                     | LOADX 00<br>LOAD 003F<br>DEC<br>LOOP@<br>LOADX 00<br>LOAD 003F                                                                                                                                                                                                                                                                                                                                                                                                | 0000 XXXX 00 XX 1 1 1<br>0000 XXXX 00 XX 1 1 1<br>0000 XXXX 00 XX 1 1 1<br>A1A1 XXXX 80 XX 0 1 0<br>0000 XXXX 00 XX 1 1 1<br>0000 XXXX 00 XX 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | loop PageSize<br>control WRITE, addr = @ + 1, DATA = ~@<br>loop PageSize                                                                                                                                                                                                          |

| 000027<br>000028<br>000029<br>00002A<br>00002B<br>00002C                                                                                     | DEC<br>LOOP@<br>RET<br>NOOP<br>NOOP<br>LOADX 00                                                                                                                                                                                                                                                                                                                                                                                                               | 0000 XXXX 00 XX 1 1 1<br>A1A1 XXXX B0 XX 0 1 0<br>0000 XXXX 00 XX 1 1 1<br>0000 XXXX 00 XX 1 1 1<br>0000 XXXX 00 XX 1 1 1<br>0000 XXXX 00 XX 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | control WRITE, addr = @ + 1, DATA = ~@<br>return<br>:Read_2_Pages<br>loop rd count jmp                                                                                                                                                                                            |

| 00002D<br>00002E<br>00002F                                                                                                                   | LOAD 001F<br>DEC<br>CJMP 002E                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000 XXXX 00 XX 1 1 1<br>A1A1 XXXX ZZ 00 1 0 0<br>A1A1 XXXX ZZ FF 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | control READ, compare InitData, addr = @ + 1<br>control READ, compare Complement, addr = @ + 1, jmp -1 ♥<br>◀                                                                                                                                                                     |

Vector Window After HT Translate Button is Pressed

Memory Test vectors are actually more like instructions for the HiLevel pin electronics, so at first they do not look like what you may expect. When you click your RUN button, the actual (and more meaningful) vectors can be seen in the Analysis window, where you@l see actual memory addresses and data. By using this Algorithmic Instruction method, very large memories can be tested with just a few hundred vectors. After creating these vectors, be sure to upload the TRN and PRG files along with the Set file.

Also See: QnApp #E1: PinList Function QnApp #E36: Memory Test Functional Description QnApp #E37: Memory Test: Flash QnApp #E43: Memory BitMap