## Q: What is Split I/O?

## Split Cycle I/O Data Format

The Split Cycle I/O mode (SCIO) allows you to switch data direction on every vector; that is *within* every vector. The typical application is to drive data to the DUT during the first part of each cycle and then compare DUT output data during the second part of each cycle. This mode also allows us to view the content of both the Stimulus RAM and the Expected Response RAM behind each tester channel.

Setup of the Pin Group is represented in this example:

| Group Order                              | 1                   | <u>•</u> |         | In SCIO we display in<br>binary and use the pin<br>name for the header.<br>We will see 2 columns<br>for each pin, one with<br>the stimulus and the |  |

|------------------------------------------|---------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Group Name                               | Data                |          |         |                                                                                                                                                    |  |

| Display                                  | Binary              | • 🔸      |         |                                                                                                                                                    |  |

| Header Mode                              | Pin Nam             | e 💌      | CopyAll | other with response.                                                                                                                               |  |

| Pin Direction                            | Split I/O           | -        |         | By using Return to Inhibit                                                                                                                         |  |

| Stimulus Forma                           | <sup>t</sup> R Inh. | ⊡ ←      |         | format, we can drive to<br>the DUT for part of each<br>vector and then switch<br>data direction for the                                            |  |

| Pins DATA0, DATA1, DATA2, DATA3,<br>Pins |                     |          |         |                                                                                                                                                    |  |

| Timing                                   | Dly                 | Value    | Unit    | Tristate the ETS pin<br>driver for the last                                                                                                        |  |

| Leading                                  | 5 🛟                 | 5        | % -     | half of each vector.                                                                                                                               |  |

| Trailing                                 | 7                   | 50       | % -     | During the last half<br>of the vector, we can<br>compare the DUT pin                                                                               |  |

| Inhibit                                  | 5 🔺                 | 5        | % -     | <ul> <li>output to the Expected<br/>Response data using</li> </ul>                                                                                 |  |

| Compare                                  | 2 -                 | 90       | % -     | the selected delay.                                                                                                                                |  |

Setting up for SCIO

It is important to insure that you are not comparing Output data during the Stimulus portion of the cycle, otherwise you will be simply õmonitoringö the tester pin driver, because your DUT output probably cannot overcome the 50 mA of drive current that the driver is providing.

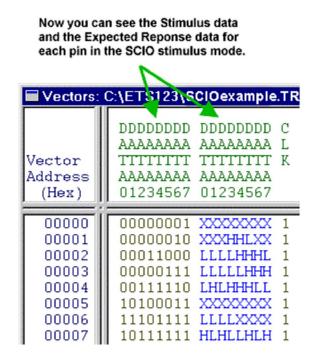

When you now look at the Vector Edit window you can see two columns of data for each pin. This data also shows Tristate and Mask information. Look at the following example:

Vectors Window using SCIO

For a better understanding of SCIO, it can be helpful to know more about the pin electronics memory. There are actually 5 RAMs behind each tester pin:

| Stimulus RAM    | (amber colored drive data)     |  |  |

|-----------------|--------------------------------|--|--|

| Response RAM    | (blue Expected Response data)  |  |  |

| Tristate RAM    | (an amber õZö)                 |  |  |

| Mask RAM        | (a blue õXö)                   |  |  |

| Acquisition RAM | (captures the DUT output data) |  |  |

When a Tristate or Mask bit is set at any given vector, it does not mean that the Stimulus or Response RAM is empty. Data is still present in the Stimulus and Response RAM at every vector, we just cannot see that data when a Z or X is displayed unless we are using SCIO. To see this data in a õnon-SCIOö mode, simply place the cursor over the Z or X and type a õUö. You can also õunmaskö or õuntristateö an entire range of vectors by using a U with the Fill command.

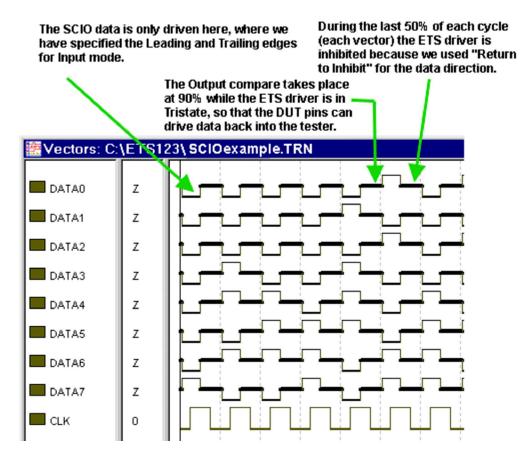

If we look at the Vector Graph while the Vectors window is open, we can see more about how the tester performs. Vector Graph can only show Stimulus data in SCIO mode, but look at the following example to learn more.

## Vector Graph showing SCIO vectors

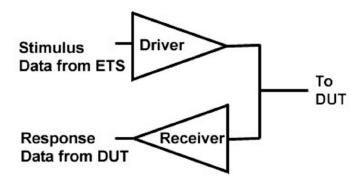

At HiLevel, we use SCIO to help verify tester functionality by driving data on each pin directly into the pinsøown receiver. This can be done entirely in software because of the design of the driver/receiver circuit:

Simplified drawing of ETS Driver/Receiver circuit

Also See: **Q'nApp #E17:** Stimulus formats **Q'nApp #E23:** Inhibit Delay **Q'nApp #E24:** Data vs. Clock **Q'nApp #E25:** Drivers and receivers **Q'nApp #E53:** Loopback